**INSTRUCTIONS MANUAL**

# LTDVE8CH-20

Strobe controller 8 CH – Firmware version 1.20

# **INDEX**

| 1. Disciaimer                               | 5  |

|---------------------------------------------|----|

| 2. Safety notes                             | 5  |

| 3. Product end-of-life handling             | 5  |

| 4. General description                      | 6  |

| 4.1. Benefits of current control            |    |

| 4.2. Operating mode                         | 6  |

| 5. Getting started                          | 6  |

| 6. Mechanical fixing                        | 7  |

| 7. Heat dissipation                         |    |

| 7.1. Calculating generated heat per channel |    |

| 7.2. Reducing generated heat                |    |

| 8. Connections                              | 8  |

| 8.1. Layout of connectors                   | 8  |

| 8.2. Power and logic supply                 | 9  |

| 8.3. Light outputs                          | 10 |

| 8.3.1. Light outputs 1 and 2                | 10 |

| 8.3.2. Light outputs 3 and 4                |    |

| 8.3.3. Light outputs 5 and 6                |    |

| 8.3.4. Light outputs 7 and 8                |    |

| 8.4. Input/output synchronization           |    |

| 8.4.1. Synchronization inputs               |    |

| 8.4.2. Synchronization outputs              |    |

| 8.4.3. Serial RS485 interface               |    |

| 8.4.4. External temperature sensor          |    |

| 8.5. Cable size and length                  |    |

| 9. Communication interfaces                 |    |

| 9.1. Serial RS485 interface                 |    |

| 9.2. Ethernet interface                     |    |

| 10. Visual indicators                       |    |

| 11. Functions of INIT button                | 19 |

| 12. Internal architecture                   |    |

| 12.1. Logic diagram                         |    |

| 12.2. Input filters                         |    |

| 12.3. Input multiplexers                    |    |

| 12.4. Pulse generator                       |    |

| 12.5. Output multiplexers                   | 23 |

| 12.6. Output protection                                     | 23 |

|-------------------------------------------------------------|----|

| 12.7. Free running oscillator                               | 25 |

| 13. Wiring diagrams                                         | 25 |

| 13.1. Wiring example #1: controller triggers camera         | 25 |

| 13.2. Wiring example #2: camera triggers controller         |    |

| 14. Operation                                               |    |

| 14.1. Operation with Modbus                                 |    |

| 14.1.1. Comparison of Modbus/RTU, Modbus/TCP and Modbus/UDP |    |

| 14.1.2. Supported function codes                            |    |

| 14.1.3. Read Holding Registers (0x03)                       |    |

| 14.1.4. Write Single Register (0x06)                        |    |

| 14.1.5. Write Multiple Registers (0x10)                     | 29 |

| 14.2. Register file                                         |    |

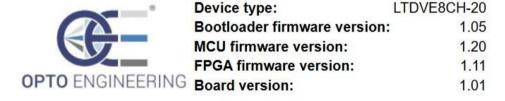

| 14.2.1. Register DEVICE_TYPE                                | 49 |

| 14.2.2. Register BOOT_VERSION                               | 49 |

| 14.2.3. Register MCU_VERSION                                | 49 |

| 14.2.4. Register FPGA_VERSION                               | 49 |

| 14.2.5. Register BOARD_VERSION                              | 49 |

| 14.2.6. Register OSC_PERIOD                                 | 49 |

| 14.2.7. Registers FILTER_SEL[0-7]                           | 49 |

| 14.2.8. Registers INPUT_SEL[0-15]                           | 50 |

| 14.2.9. Registers GEN_DELAY_BASE[0-15]                      |    |

| 14.2.10. Registers GEN_DELAY_COUNT[0-15]                    |    |

| 14.2.11. Registers GEN_WIDTH_BASE[0-15]                     |    |

| 14.2.12. Registers GEN_WIDTH_COUNT[0-15]                    | 53 |

| 14.2.13. Registers OUTPUT_SEL_HI[0-15]                      |    |

| 14.2.14. Registers OUTPUT_SEL_LO[0-15]                      |    |

| 14.2.15. Registers PRT_CNT_ON[0-7]                          |    |

| 14.2.16. Registers PRT_ENA_ON[0-7]                          |    |

| 14.2.17. Registers PRT_CNT_OFF[0-7]                         |    |

| 14.2.18. Registers PRT_ENA_OFF[0-7]                         |    |

| 14.2.19. Registers CUR_RANGE[0-7]                           |    |

| 14.2.20. Registers CUR_VALUE[0-7]                           |    |

| 14.2.21. Register RS485_MODBUS_ADDR                         |    |

| 14.2.22. Register RS485_LINE_SPEED                          |    |

| 14.2.23. Register RS485_LINE_PARITY                         |    |

| 14.2.24. Registers ETH_MAC_ADDR[0-2]                        |    |

| 14.2.25. Registers ETH_HOSTNAME[0-7]                        |    |

| 14.2.26. Register ETH DHCP ENABLE                           | 60 |

| 14.2.27   | Register ETH_IP_ADDR_HI           | 60 |

|-----------|-----------------------------------|----|

| 14.2.28   | Register ETH_IP_ADDR_LO           | 60 |

| 14.2.29   | Register ETH_SUBNET_MASK_HI       | 60 |

| 14.2.30   | Register ETH_SUBNET_MASK_LO       | 60 |

| 14.2.31   | . Register ETH_DEF_GATEWAY_HI     | 60 |

| 14.2.32   | Register ETH_DEF_GATEWAY_LO       | 61 |

| 14.2.33   | Register ETH_PRI_DNS_HI           | 61 |

|           | . Register ETH_PRI_DNS_LO         |    |

|           | Register ETH_SEC_DNS_HI           |    |

| 14.2.36   | Register ETH_SEC_DNS_LO           | 61 |

| 14.2.37   | . Register ETH_MODBUS_ADDR        | 61 |

| 14.2.38   | Register ETH_MODBUS_TCP_PORT      | 61 |

| 14.2.39   | . Register ETH_MODBUS_UDP_PORT    | 62 |

| 14.2.40   | . Registers WEB_PASSWORD[0-3]     | 62 |

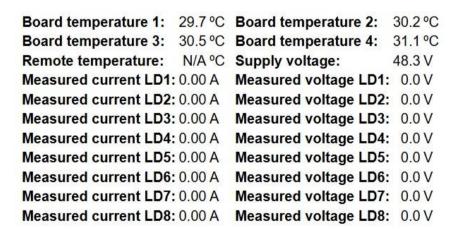

| 14.2.41   | . Register BOARD_TEMPERATURE[0-3] | 62 |

| 14.2.42   | Register REMOTE_TEMPERATURE       | 62 |

| 14.2.43   | . Register SUPPLY_VOLTAGE         | 62 |

| 14.2.44   | . Registers MEASURED_CURRENT[0-7] | 63 |

| 14.2.45   | Registers MEASURED_VOLTAGE[0-7]   | 63 |

| 14.2.46   | Register ERROR_WORD               | 64 |

| 14.2.47   | Registers GEN_HOLD_BASE[0-15]     | 64 |

| 14.2.48   | Registers GEN_HOLD_COUNT[0-15]    | 65 |

| 14.2.49   | Registers GEN_EDGE_SEL[0-15]      | 66 |

| 14.2.50   | Registers POLARITY_SEL[0-7]       | 66 |

| 14.2.51   | . Registers DRIVE_TIME[0-7]       | 67 |

| 14.2.52   | Registers CUR_RED_DELAY[0-7]      | 67 |

| 14.2.53   | Registers CUR_RED_VALUE[0-7]      | 68 |

| 14.2.54   | . Register SOFTWARE_TRIGGER       | 68 |

| 14.2.55   | Registers CAL_XXX                 | 68 |

| 14.2.56   | Registers CAL_UNLOCK_CODE[0-1]    | 69 |

| 14.2.57   | . Register BOARD_COMMAND          | 69 |

| 14.3. Ope | ration with a web browser         | 69 |

| 14.3.1.   | Main page and navigation menu     | 69 |

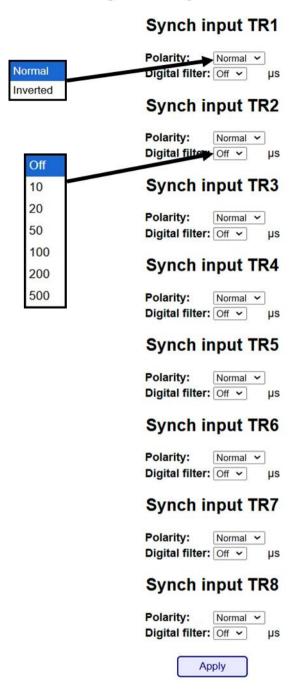

| 14.3.2.   | Setup synch inputs TR1-TR8        | 72 |

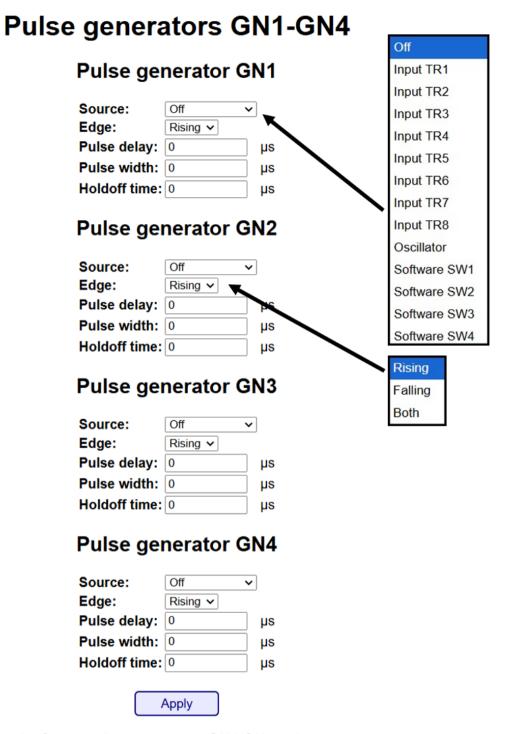

| 14.3.3.   | Setup pulse generators GN1-GN4    | 74 |

| 14.3.4.   | Setup pulse generators GN5-GN8    | 76 |

| 14.3.5.   | Setup pulse generators GN9-GN12   | 76 |

| 14.3.6.   | Setup pulse generators GN13-GN16  | 76 |

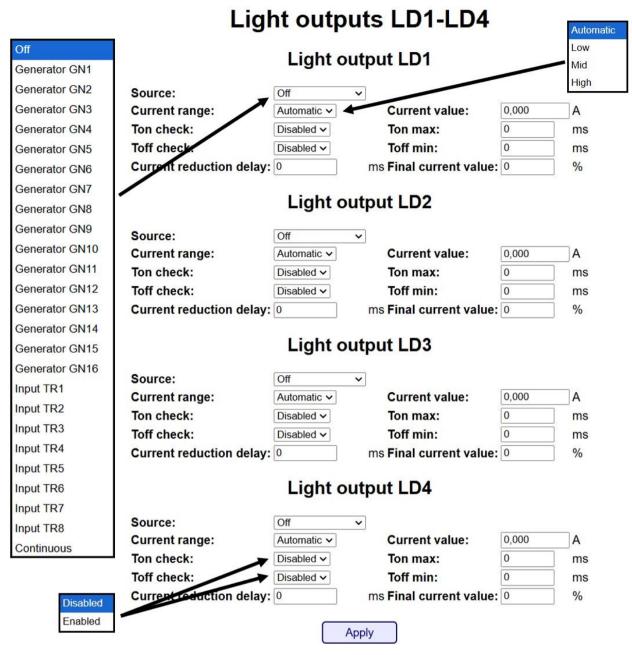

| 14.3.7.   | Setup light outputs LD1-LD4       | 76 |

| 78 |

|----|

| 78 |

| 80 |

| 80 |

| 82 |

| 84 |

| 84 |

| 87 |

| 88 |

| 90 |

| 90 |

| 99 |

|    |

#### 1. Disclaimer

Always deploy and store Opto Engineering products in the prescribed conditions in order to ensure proper functioning. Failing to comply with the following conditions may shorten the product lifetime and/or result in malfunctioning, performance degradation or failure.

Ensure that incorrect functioning of this equipment cannot cause any dangerous situation or significant financial loss to occur. It is essential that the user ensures that the operation of the controller is suitable for their application. All trademarks mentioned herein belong to their respective owners.

Except as prohibited by law:

- All hardware, software and documentation are provided on an "as is" basis

- · Opto Engineering accepts no liability for consequential loss, of any kind

Upon receiving your Opto Engineering product, visually examine the product for any damage during shipping. If the product is damaged upon receipt, please notify Opto Engineering immediately.

### 2. Safety notes

Please read the following notes before using this controller. Contact your distributor or dealer for any doubts or further advice.

This device must not be used in an application where its failure could cause a hazard to human health or damage to other equipment. Keep in mind that if the device is used in a manner not foreseen by the manufacturer, the protection provided by its circuits and by its enclosure may be impaired.

This is a low voltage device. As such, the potential difference between any combination of applied signals must not exceed, at all times, the supply voltage. Higher voltages may cause a fault and can be dangerous to human health.

This device has limited protection against transients caused by inductive loads. If necessary, use external protection devices like fast diodes or, better, specific transient protectors.

The controller outputs pulses with high energy content. The user must be careful to connect the inputs and outputs correctly and to protect the output wiring and load from unintentional short-circuits. When the device is switched off, there is still energy stored in the internal capacitors for at least five minutes.

When operating the controller at the maximum ratings it can get very hot. The controller should be positioned where personnel cannot accidentally touch it and away from flammable materials. Never exceed the power ratings stated in the manual.

# 3. Product end-of-life handling

Observe the following guidelines when recycling this equipment or its components.

Production of this equipment required the extraction and use of natural resources. The equipment may contain substances that could be harmful to the environment or human health if improperly handled at the product's end of life. In order to avoid release of such substances into the environment and to reduce the use of natural resources, we encourage you to recycle this product in an appropriate system that will ensure that most of the materials are reused or recycled appropriately.

This symbol indicates that this product complies with the applicable European Union requirements according to the WEEE (Waste Electrical and Electronic Equipment) Directive 2012/19/EU

### 4. General description

Any machine vision application employs some kind of light controller. Light controllers are widely used to both optimize illumination intensity and obtain repeatable trigger sequencing between lights and vision cameras.

This controller is a compact unit that includes power supply conditioning, intensity control, timing generation and advanced triggering functions.

The controller can be set up using a PC with serial RS485 or Ethernet interfaces. Configurations are saved in non-volatile memory so that the controller will resume operation after a power cycle.

For older firmware versions, please contact us on <a href="www.opto-e.com">www.opto-e.com</a> to receive the corresponding manual.

#### 4.1. Benefits of current control

Most LED manufacturers suggest their products to be driven using a constant current source, not a constant voltage source. This is because, using a constant voltage driving, small variations in temperature or voltage at the LEDs can cause a noticeable change in their brightness.

Brightness control with voltage is also very difficult because of the non-linearity of brightness with voltage. On the contrary, the brightness is approximately linear with current, so by driving the LEDs with a known current, intensity control is linear.

### 4.2. Operating mode

This strobe controller has eight independent, programmable, current-controlled light outputs. The eight light outputs can be used in pulsed or continuous mode.

In pulsed mode the light is switched on only when necessary. A digital input is used as a trigger source. When a rising or falling edge on the trigger signal is detected the output is pulsed for the programmed amount of time.

Using this technique, it is possible to obtain excellent steady images of moving objects. The camera can be set for an arbitrary long exposure time and the light turned on for a shorter time, just enough to freeze the motion. This helps to overcome the uncertainty issues usually related with integration start which, to some degree, afflict most commercial cameras.

The delay from the trigger to the output pulse, the width of the output pulse and the intensity of the output pulse are all independently configurable. The pulse delay can range from 0  $\mu$ s to 1 s. The pulse width can range from 1  $\mu$ s to 1 s.

In continuous mode the light is always switched on, independently from the trigger signal. Using this technique, the maximum current value for each channel has to be limited in order to prevent the overheating of the controller.

There are three current ranges. They are:

- Low current, up to 200 mA (with resolution of 1 mA)

- Mid current, up to 4 A (with resolution of 4 mA)

- High current, up to 20 A (with resolution of 20 mA)

The controller must be powered with a fixed supply voltage between 24 V and 48 V DC. This allows a large number of different lights to be efficiently driven.

For more information about current and power limitations refer to chapter 7.

# 5. Getting started

Carefully read the sections on Safety Notes and Heat Dissipation and check the product fits your

needs. Mount the controller using a DIN rail as described in the section on Mechanical fixing.

Connect the controller as in the section on <u>Connections</u>. When the controller powers up it should show the PWR LED lit with a stable green colour and the RUN LED lit with a flashing green colour.

Read the section on <u>Operation</u>. The controller can be configured by using both a serial RS485 interface and an Ethernet interface (see <u>chapter 9</u>).

### 6. Mechanical fixing

The controller must be mounted on a DIN rail. Allow free flow of air around the unit. The controller has an IP rating of 20 and should be installed so that moisture and dirt cannot enter it.

An enclosure may also be required for other parts of the system such as power supplies. That enclosure would provide both mechanical and environmental protection in industrial applications.

### 7. Heat dissipation

The controller integrates several linear circuits to produce the constant current outputs. This means that it generates heat which needs to be dissipated. The operating temperature range is  $0~^{\circ}$ C to  $40~^{\circ}$ C.

The controller can approximately dissipate the following average powers:

- 30 W at 25 °C (about 3.8 W per channel)

- 25 W at 40 °C (about 3.1 W per channel)

A simple way to estimate the maximum average power the controller can dissipate is by applying the following formula:

DissipablePower [W] =  $(TempHeatsink [^{\circ}C] - TempAmbient [^{\circ}C]) / ThResistance [^{\circ}C/W]$

#### Where:

- DissipablePower is the maximum average power the controller can dissipate

- TempHeatsink is the maximum temperature of the controller heatsink

- TempAmbient is the actual temperature of the ambient where the controller is placed

- ThResistance is the thermal resistance between the heatsink and the ambient

For this controller the *ThResistance* parameter is about 1.91 °C/W.

The maximum permissible controller heatsink temperature is 90  $^{\circ}$ C. If the heatsink temperature rises above 90  $^{\circ}$ C, the controller switches off all the output channels. The output channels are then reactivated once temperature falls below 80  $^{\circ}$ C.

If the average power that must be dissipated is greater than the previously stated value, a different and more efficient cooling system is required. Solutions could be the use of a cooling fan (active cooling system) or the use of a bigger heatsink (passive cooling system).

The controller must be powered with a fixed supply voltages between 24 V and 48 V DC. Take care of the actual supply voltage when calculating the generated heat.

# 7.1. Calculating generated heat per channel

For a pulsed output, the average power that is transformed to heat and then must be dissipated can be calculated using the following formula:

Heat [W] = LightCurrent [A] \* (SupplyVoltage [V] – LightVoltage [V]) \* DutyCycle [·]

#### Where:

• LightCurrent is the illuminator operating current

- LightVoltage is the illuminator operating voltage

- SupplyVoltage is the actual supply voltage (from 24 V to 48 V)

- DutyCycle is the actual duty cycle

The duty cycle is given by:

DutyCycle [·] = PulseWidth [s] \* TriggerFrequency [Hz]

If the output is driven in continuous mode, the previous equations are still valid but the parameter *DutyCycle* becomes 1.0 because the output is always active.

The parameters *LightCurrent* and *LightVoltage* are light specific and should be either given in the light documentation or measured experimentally.

### 7.2. Reducing generated heat

The total heat generated by the controller is simply given by adding the generated heat for each of the eight channels, as calculated in the previous section.

There are several ways to reduce the heat generated by the controller. The simplest way would be to turn the light off when not needed. If the light is on only when necessary, the generated heat can be drastically diminished. Another opportunity would be to reduce pulse width or output current, if permitted by the application.

Another strategy to reduce the generated heat would be to connect lights in series instead of parallel, if possible. If you have several lights connected in parallel then changing the arrangement to series will increase the voltage across them but also reduce the overall current.

The last option, feasible with this eight channels controller, would be to use two or more controllers and use just a few channels from each. For high power applications this may be the only solution.

#### 8. Connections

See the next sections for information about connections. Power supply and light output connections are made via screw terminals on the bottom-side panel of the controller. Check all connections carefully before switching on the equipment.

The controller has two 24 V to 48 V DC power supplies: a dedicated power supply for the power stages and a dedicated power supply for the logic section. This is to increase versatility.

Inside the controller, supply to the logic circuits is derived using a pair of diodes from both of these power supplies. This means that either of the two supplies can power the logic circuits.

Ideally, supply to the power stages could be removed at any time to protect the end user from photobiological and other hazards that can occur during fault conditions. Should supply to the power stages be removed while the system is running, the system designer may consider providing the dedicated logic supply to keep the controller powered and responsive.

For convenience, the two power supplies share a single, common negative terminal.

### 8.1. Layout of connectors

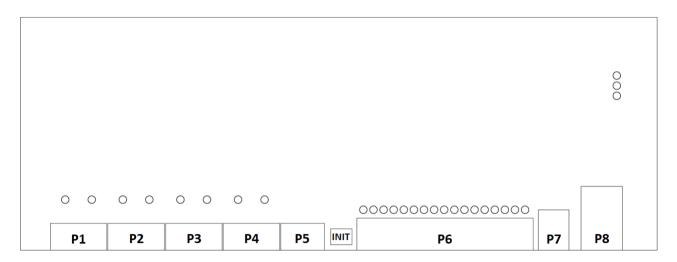

The drawing in *Figure 1: connectors on the controller front panel* depicts all the controller connections, which are easily accessible on the bottom-side panel. As indicated in the drawing, connectors are identified by their unique designators (P1, P2, P3, P4, P5, P6, P7 and P8).

Figure 1: connectors on the controller front panel

The connectors are briefly described below. A detailed description follows in the next sections.

- Connectors P1, P2, P3 and P4 are used to connect the eight lights

- Connector P5 is used to supply power

- Connector P6 is used for input/output synchronization and for serial RS485 communication

- Connector P7 is a USB port (B type), not active at the moment

- Connector P8 is an Ethernet RJ45 jack

For connectors P1, P2, P3, P4, P5 and P6 a mating plug is provided in the controller package. For convenience the relevant manufacturer part numbers are listed in *Table 1: mating plugs for the controller connectors*. Even if equivalent mating plugs may be available, these are the recommended components.

| Connector designator | Manufacturer    | Mating plug part number |

|----------------------|-----------------|-------------------------|

| P1, P2, P3, P4       | Phoenix Contact | 1757035                 |

| P5                   | Phoenix Contact | 1757022                 |

| P6                   | MH Connectors   | MHDB37SS                |

Table 1: mating plugs for the controller connectors

# 8.2. Power and logic supply

The power supply voltage must be between 24 V and 48 V DC. A dedicated and well-regulated switching power supply is required. The external power supply must be capable of supplying the average and peak currents needed for all active light outputs.

Choose a power supply unit that limits its output current by design or use protecting fuses. The fuses should be appropriately de-rated if mounted in an enclosure, as the inside temperature can be higher than the ambient temperature.

Ensure that the wire gauge used for these power connections is appropriate for the current to be drawn. The power supply low voltage and mains wiring should be separately routed.

Power supply is delivered to the controller using the screw terminals of connector P5. Connector pinout, ordered from left to right, is listed in *Table 2: pinout of connector P5*.

| Number | Name   | Description                     | Note                   |

|--------|--------|---------------------------------|------------------------|

| 1      | +V LOG | Power supply. Positive terminal | Used for logic section |

| 2      | 0V     | Power supply. Negative terminal |                        |

| 3      | +V PWR | Power supply. Positive terminal | Used for power stages  |

Table 2: pinout of connector P5

The controller has two 24 V to 48 V power terminals to independently supply the logic and power sections inside the unit. They are named +V LOG and +V PWR. These two supplies can be connected together or separately, as required by the application. They share the common negative terminal named 0V. It must be connected to the power supply negative.

Ensure that the polarity of +V LOG, +V PWR and 0V is correct before applying power.

### 8.3. Light outputs

Light outputs are paired on the four 4-way pluggable screw terminal sockets named P1, P2, P3 and P4. It is possible to use two 2-way connectors in a 4-way socket. The light output connections must not be paralleled or grounded in any way.

The state of each output is shown by a yellow LED indicator next to the connector.

Make sure you set the correct current rating for a light before using it. See the light datasheet and manual for details on this topic.

### 8.3.1. Light outputs 1 and 2

Light outputs 1 and 2 are available on the LD1+, LD1-, LD2+ and LD2- screw terminals of connector P1. Connector pinout, ordered from left to right, is listed in *Table 3: pinout of connector P1*. Be careful not to cross-connect the two lights.

| Number | Name | Description Note                    |  |

|--------|------|-------------------------------------|--|

| 1      | LD1+ | Power channel 1 output. LED anode   |  |

| 2      | LD1- | Power channel 1 output. LED cathode |  |

| 3      | LD2+ | Power channel 2 output. LED anode   |  |

| 4      | LD2- | Power channel 2 output. LED cathode |  |

Table 3: pinout of connector P1

Please note that LED1- and LED2- are not the same as 0V.

# 8.3.2. Light outputs 3 and 4

Light outputs 3 and 4 are available on the LD3+, LD3-, LD4+ and LD4- screw terminals of connector P2. Connector pinout, ordered from left to right, is listed in *Table 4: pinout of connector P2*. Be careful not to cross-connect the two lights.

|        |      | <b>5</b>    |      |

|--------|------|-------------|------|

| Number | Name | Description | Note |

|        |      |             |      |

| 1 | LD3+ | Power channel 3 output. LED anode   |  |

|---|------|-------------------------------------|--|

| 2 | LD3- | Power channel 3 output. LED cathode |  |

| 3 | LD4+ | Power channel 4 output. LED anode   |  |

| 4 | LD4- | Power channel 4 output. LED cathode |  |

Table 4: pinout of connector P2

Please note that LED3- and LED4- are not the same as 0V.

### 8.3.3. Light outputs 5 and 6

Light outputs 5 and 6 are available on the LD5+, LD5-, LD6+ and LD6- screw terminals of connector P3. Connector pinout, ordered from left to right, is listed in *Table 5: pinout of connector P3*. Be careful not to cross-connect the two lights.

| Number | Name | <b>Description</b> Note             |  |

|--------|------|-------------------------------------|--|

| 1      | LD5+ | Power channel 5 output. LED anode   |  |

| 2      | LD5- | Power channel 5 output. LED cathode |  |

| 3      | LD6+ | Power channel 6 output. LED anode   |  |

| 4      | LD6- | Power channel 6 output. LED cathode |  |

Table 5: pinout of connector P3

Please note that LED5- and LED6- are not the same as 0V.

# 8.3.4. Light outputs 7 and 8

Light outputs 7 and 8 are available on the LD7+, LD7-, LD8+ and LD8- screw terminals of connector P4. Connector pinout, ordered from left to right, is listed in *Table 6: pinout of connector P4*. Be careful not to cross-connect the two lights.

| Number | Name | <b>Description</b> Note             |  |

|--------|------|-------------------------------------|--|

| 1      | LD7+ | Power channel 7 output. LED anode   |  |

| 2      | LD7- | Power channel 7 output. LED cathode |  |

| 3      | LD8+ | Power channel 8 output. LED anode   |  |

| 4      | LD8- | Power channel 8 output. LED cathode |  |

Table 6: pinout of connector P4

Please note that LED7- and LED8- are not the same as 0V.

### 8.4. Input/output synchronization

Connector P6 is used for input and output synchronization and for serial RS485 communication.

There are eight independent, galvanically isolated, synchronization inputs. These inputs can be connected directly to the system for voltages up to 24 V. An external series resistor is not necessary.

The synchronization inputs may be left unconnected when not used. The state of each synchronization input is shown by a green LED indicator next to the connector.

There are eight independent, galvanically isolated, synchronization outputs. These outputs can be used, for example, to trigger a camera or a slave controller. These outputs can be connected directly to the system for voltages up to 30 V. The state of each synchronization output is shown by a yellow LED indicator next to the connector.

Connector P6 also provides three signals for an electrically isolated serial RS485 interface and two signals for an optional and non-electrically isolated external temperature sensor. The activity of the serial RS485 interface is shown by a dedicated yellow LED next to connector P6.

See the following section for more information about connector P6.

### 8.4.1. Synchronization inputs

The eight synchronization inputs are available on the TR1+, TR1-, TR2+, TR2-, TR3+, TR3-, TR4+, TR4-, TR5+, TR5-, TR6+, TR6-, TR7+, TR7-, TR8+ and TR8- terminals of connector P6. These signals are listed in the *Table 7: pinout of connector P6 for synchronization inputs*. Be careful not to cross-connect the eight synchronization inputs.

| Pin number | Name | Description                |

|------------|------|----------------------------|

| 1          | TR1- | Input 1. Negative terminal |

| 20         | TR1+ | Input 1. Positive terminal |

| 2          | TR2- | Input 2. Negative terminal |

| 21         | TR2+ | Input 2. Positive terminal |

| 3          | TR3- | Input 3. Negative terminal |

| 22         | TR3+ | Input 3. Positive terminal |

| 4          | TR4- | Input 4. Negative terminal |

| 23         | TR4+ | Input 4. Positive terminal |

| 5          | TR5- | Input 5. Negative terminal |

| 24         | TR5+ | Input 5. Positive terminal |

| 6          | TR6- | Input 6. Negative terminal |

| 25         | TR6+ | Input 6. Positive terminal |

| 7          | TR7- | Input 7. Negative terminal |

| 26         | TR7+ | Input 7. Positive terminal |

| 8          | TR8- | Input 8. Negative terminal |

| 27         | TR8+ | Input 8. Positive terminal |

Table 7: pinout of connector P6 for synchronization inputs

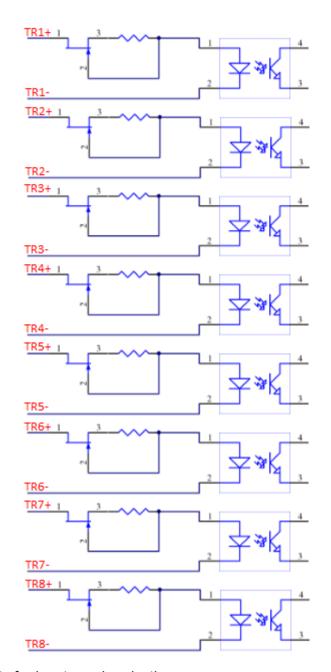

The schematic of *Figure 2: interface circuits for input synchronization* depicts the internal input circuits. An internal constant current generator connected in series with each input allows for a broad range of input voltages without any need for a series resistor. These inputs can be directly driven by voltages up to 24 V.

Figure 2: interface circuits for input synchronization

Circuit specifications are summarized in *Table 8: specifications of input synchronization circuits*. Please note the reported values are typical.

| Parameter  | Value    | Unit | Note                                |

|------------|----------|------|-------------------------------------|

| Uin (low)  | 0 – 1    | V    | -                                   |

| Uin (high) | 3.3 – 24 | V    | -                                   |

| lin        | 5 – 9    | mA   | Internal constant-current generator |

Table 8: specifications of input synchronization circuits

### 8.4.2. Synchronization outputs

The eight synchronization outputs are available on the SH1+, SH1-, SH2+, SH2-, SH3+, SH3-, SH4+, SH4-, SH5+, SH5-, SH6+, SH6-, SH7+, SH7-, SH8+ and SH8- terminals of connector P6. These signals are listed in the *Table 9: pinout of connector P6 for synchronization outputs*. Be careful not to cross-connect the eight synchronization outputs.

| Pin number | Name | Description                  |

|------------|------|------------------------------|

| 9          | SH1- | Output 1. Emitter terminal   |

| 28         | SH1+ | Output 1. Collector terminal |

| 10         | SH2- | Output 2. Emitter terminal   |

| 29         | SH2+ | Output 2. Collector terminal |

| 11         | SH3- | Output 3. Emitter terminal   |

| 30         | SH3+ | Output 3. Collector terminal |

| 12         | SH4- | Output 4. Emitter terminal   |

| 31         | SH4+ | Output 4. Collector terminal |

| 13         | SH5- | Output 5. Emitter terminal   |

| 32         | SH5+ | Output 5. Collector terminal |

| 14         | SH6- | Output 6. Emitter terminal   |

| 33         | SH6+ | Output 6. Collector terminal |

| 15         | SH7- | Output 7. Emitter terminal   |

| 34         | SH7+ | Output 7. Collector terminal |

| 16         | SH8- | Output 8. Emitter terminal   |

| 35         | SH8+ | Output 8. Collector terminal |

Table 9: pinout of connector P6 for synchronization outputs

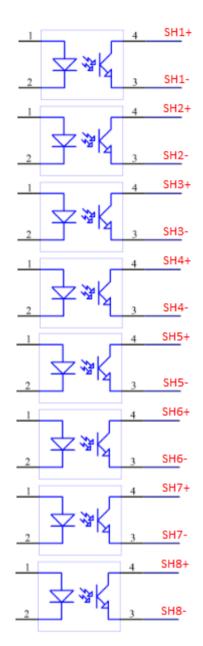

The schematic of *Figure 3: interface circuits for output synchronization* depicts the internal output circuits. These outputs can be directly connected to voltages up to 30 V.

Figure 3: interface circuits for output synchronization

Circuit specifications are summarized in *Table 10: specifications of output synchronization circuits*. Please note the reported values are typical.

| Parameter  | Value | Unit | Note |

|------------|-------|------|------|

| lout (typ) | 10    | mA   | -    |

| lout (max) | 15    | mA   | -    |

| Uout (max) | 30    | V    | -    |

Table 10: specifications of output synchronization circuits

### 8.4.3. Serial RS485 interface

The serial interface is available on the D+, D- and GND terminals of connector P6. These signals

are listed in *Table 11: pinout of serial interface in connector P6*. Be careful not to cross-connect the serial interface signals.

| Pin number | Name | Description                          | Note |

|------------|------|--------------------------------------|------|

| 18         | D-   | RS485 data signal. Negative terminal | -    |

| 19         | GND  | RS485 reference ground               | -    |

| 37         | D+   | RS485 data signal. Positive terminal | -    |

Table 11: pinout of serial interface in connector P6

The interface is electrically isolated. Note that GND is not the same as 0V.

### 8.4.4. External temperature sensor

The controller allows for the connection of one external temperature sensor. The intended temperature sensing element is a NTC (Negative Temperature Coefficient) thermistor with coefficients  $R_{25}$  = 10 k $\Omega$  and  $B_{25/85}$  = 3610 K. A suitable component is the Vishay NTCS0603E3103FMT.

The signals are listed in *Table 12: pinout of external temperature sensor in connector P6*. The two terminals can be connected freely to the external thermistor, as the component is not polarized.

| Pin number | Name  | Description                   |

|------------|-------|-------------------------------|

| 17         | NTC_A | Temperature sensor terminal A |

| 36         | NTC_B | Temperature sensor terminal B |

Table 12: pinout of external temperature sensor in connector P6

These analogue signals are not electrically isolated from the controller electronics. Be careful not to connect them to any other signal. A severe malfunction or even a short circuit may occur.

# 8.5. Cable size and length

The actual connecting cables must be chosen on the basis of their load sinking current, the length, the working voltage and the cable materials characteristics. Special ambient conditions may further restrict the choice to a specific kind of cable.

The *Table 13: cable wire size and length* lists the recommended wire sizes and maximum allowed lengths for all the cables coming to and leaving from the controller. American Wire Gauge (AWG) is the wire measurement system used by the United States and Canada, while mm is the metric system of measurement used across Europe and in most of the world.

| Do et                  | Recommen | ded wire size | Maximum langth [m] |

|------------------------|----------|---------------|--------------------|

| Port                   | mm²      | AWG           | Maximum length [m] |

| Power and logic supply | 1.5      | 15            | 5                  |

| Light outputs          | 0.75     | 18            | 5                  |

| Synchronization inputs | 0.25     | 24            | 5                  |

| Synchronization outputs     | 0.25 | 24 | 5 |

|-----------------------------|------|----|---|

| Serial RS485 interface      | 0.25 | 24 | 5 |

| External temperature sensor | 0.25 | 24 | 5 |

Table 13: cable wire size and length

For improved immunity against external disturbance sources, use a single shielded cable or multiple shielded cables, grounded at the end opposite to the controller, on the synchronization inputs, synchronization outputs, serial RS485 interface and external temperature sensor signals.

For the lights use cables as short as possible and with appropriate wire size. Cable reactance limits performance in pulsed mode, consider to reduce its value by connecting two or more smaller wires in parallel. For long cables it is recommended to raise the voltage of the illumination. This can be realized by selecting lights with LEDs connected in series rather than connected in parallel.

#### 9. Communication interfaces

There are several ways to configure the controller.

A first option is to use the serial RS485 interface. To support this interface the controller implements a subset of the Modbus/RTU (Remote Terminal Unit) slave protocol.

A second option is to use the Ethernet interface. Supported Ethernet speeds are 10 Mbit/s and 100 Mbit/s with auto negotiation. The Ethernet interface allows to configure the controller using the Modbus/TCP (Transmission Control Protocol) slave protocol, the Modbus/UDP (User Datagram Protocol) slave protocol or the HTTP (Hyper Text Transfer Protocol) protocol. For supporting the latter, the controller provides an internal web server accessible by most common web browsers.

The Modbus/RTU, Modbus/TCP and Modbus/UDP protocols are implemented by most programmable logic controllers (PLCs) with a suitable interface.

The availability of two physical interfaces and four logical protocols makes it easy to integrate the controller in most vision applications.

See chapter 14 for details on operation with both Modbus and web browser.

#### 9.1. Serial RS485 interface

For the serial RS485 interface, the controller implements a subset of the Modbus/RTU slave protocol and operates, by default, at 9600 bits per second with even parity. The factory set Modbus address is 32 and it is saved in the controller non-volatile memory.

The Modbus address is one of the controller parameters and can be changed using any of the available interfaces. The factory set Modbus address can be restored using the INIT button (see <a href="https://change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.change.c

Please note valid Modbus addresses for slave devices are in the range 1 to 247; remaining addresses are reserved by the standard for special purposes and must not be used. It is of great importance to ensure, at the time of assigning the slave address, that there are not two devices with the same address. In such a case, an abnormal behaviour of the whole serial bus can occur, the master being then in the impossibility to communicate with all the slaves present on the bus.

The activity of the serial RS485 interface is shown by a dedicated yellow LED next to connector P6.

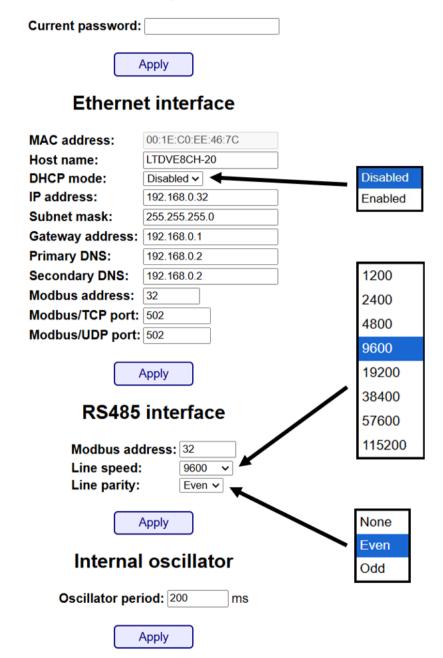

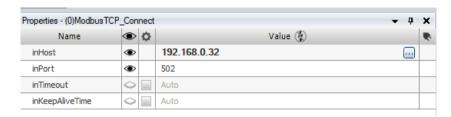

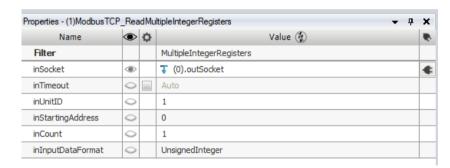

#### 9.2. Ethernet interface

The Ethernet interface allows to configure the controller using the Modbus/TCP slave protocol, the Modbus/UDP slave protocol or the HTTP protocol. For the last option, the controller provides an internal web server accessible by most common web browsers.

To use the interface, connect the controller using a standard Ethernet cable. The default parameters for the communication are listed in *Table 14: default parameters for Ethernet communication*.

| Parameter            | Default Value |

|----------------------|---------------|

| Host name            | LTDVE8CH-20   |

| DHCP                 | Disabled      |

| IP address           | 192.168.0.32  |

| Subnet mask          | 255.255.255.0 |

| Default gateway      | 192.168.0.1   |

| Preferred DNS server | 192.168.0.2   |

| Alternate DNS server | 192.168.0.2   |

| Modbus address       | 32            |

| Modbus/TCP port      | 502           |

| Modbus/UDP port      | 502           |

Table 14: default parameters for Ethernet communication

The IP address, subnet mask and DHCP use flag are some of the controller parameters and can be changed using any of the available interfaces. The factory configuration uses the static IP address 192.168.0.32. The factory settings can be restored using the INIT button (see <a href="https://creativecommons.org/charge-chapter-11">chapter 11</a> for a description of the INIT button functionalities).

#### 10. Visual indicators

There are twenty-eight LEDs on the top panel of the controller and two LEDs embedded in the Ethernet RJ45 jack. Some of them are used to show that power supplies are available, others are pulsed when inputs and output are activated, while others are used to indicate activity on the communication interfaces or fault conditions.

The exact meaning of each of the LEDs is listed in *Table 15: meaning of the LEDs*. The LEDs of the top panel of the controller are identified by a unique label printed next to them. The Ethernet ACT and LINK LEDs are identified by their position relative to the Ethernet RJ45 jack. The ACT LED is at the left of the jack, while the LINK LED is at the right.

| Number | Name | Colour | Description                                                  |  |

|--------|------|--------|--------------------------------------------------------------|--|

| 1      | PWR  | Green  | Stable when logic supply is present                          |  |

| 2      | RUN  | Green  | Blinks periodically during normal operation                  |  |

| 3      | ERR  | Red    | Stable when power supply missing, blinks in error conditions |  |

| 4      | LD1  | Yellow | Pulses when light output 1 is activated                      |  |

| 5      | LD2  | Yellow | Pulses when light output 2 is activated                      |  |

| 6      | LD3  | Yellow | Pulses when light output 3 is activated                      |  |

| 7      | LD4  | Yellow | Pulses when light output 4 is activated                      |  |

| 8      | LD5  | Yellow | Pulses when light output 5 is activated                      |  |

| 9      | LD6  | Yellow | Pulses when light output 6 is activated                      |  |

| 10     | LD7  | Yellow | Pulses when light output 7 is activated                      |  |

| 11     | LD8  | Yellow | Pulses when light output 8 is activated                      |  |

| 12     | TR1  | Green  | Pulses when synchronization input 1 is activated             |  |

| 13 | TR2  | Green  | Pulses when synchronization input 2 is activated      |  |

|----|------|--------|-------------------------------------------------------|--|

| 14 | TR3  | Green  | Pulses when synchronization input 3 is activated      |  |

| 15 | TR4  | Green  | Pulses when synchronization input 4 is activated      |  |

| 16 | TR5  | Green  | Pulses when synchronization input 5 is activated      |  |

| 17 | TR6  | Green  | Pulses when synchronization input 6 is activated      |  |

| 18 | TR7  | Green  | Pulses when synchronization input 7 is activated      |  |

| 19 | TR8  | Green  | Pulses when synchronization input 8 is activated      |  |

| 20 | SH1  | Yellow | Pulses when synchronization output 1 is activated     |  |

| 21 | SH2  | Yellow | Pulses when synchronization output 2 is activated     |  |

| 22 | SH3  | Yellow | Pulses when synchronization output 3 is activated     |  |

| 23 | SH4  | Yellow | Pulses when synchronization output 4 is activated     |  |

| 24 | SH5  | Yellow | Pulses when synchronization output 5 is activated     |  |

| 25 | SH6  | Yellow | Pulses when synchronization output 6 is activated     |  |

| 26 | SH7  | Yellow | Pulses when synchronization output 7 is activated     |  |

| 27 | SH8  | Yellow | Pulses when synchronization output 8 is activated     |  |

| 28 | 485  | Yellow | Blinks when there is activity on the serial interface |  |

| 29 | ACT  | Yellow | Blinks during Ethernet data transmission              |  |

| 30 | LINK | Green  | Stable when Ethernet connection established           |  |

Table 15: meaning of the LEDs

Either the RUN LED or the ERR LED blinks for 500 ms at power on to identify the source of data used for the settings.

The green RUN LED blinks when the controller powers up using the settings stored in the non-volatile memory (the last configuration saved by the customer). The red ERR LED blinks when the controller reverts to using the factory settings due to user activation of the INIT button (see next section for more information on the INIT button) or a corruption in the stored customer settings.

Please note the logic supply must be present in order for all the LEDs to turn on.

#### 11. Functions of INIT button

The INIT button is used either to restore the factory settings or to activate the firmware update procedure.

To restore the factory settings, follow these steps:

- 1. Switch off the device and wait 30 seconds

- 2. Push and hold down the INIT button

- 3. Switch on the device

- 4. Release the INIT button

- 5. Wait 10 seconds

After the ten seconds interval the settings are restored to the factory values and the controller resumes normal operation.

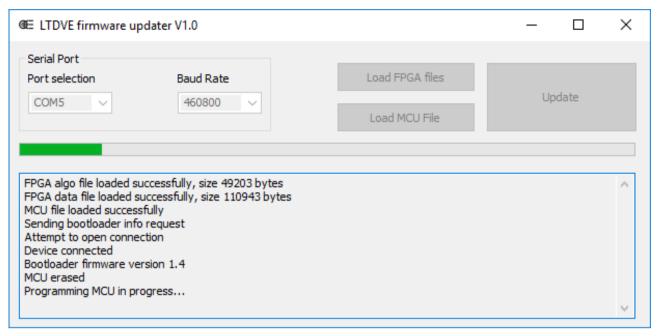

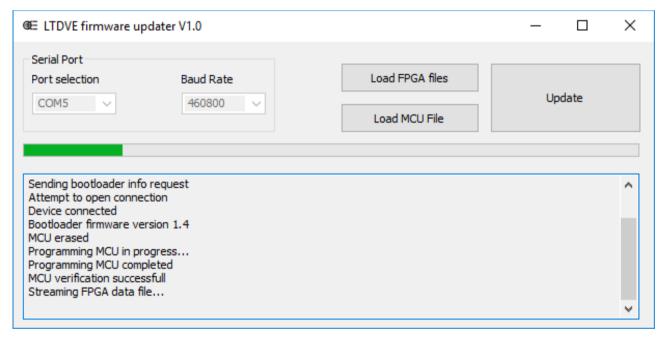

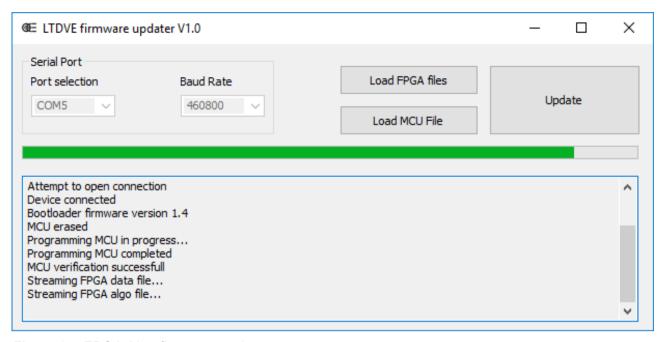

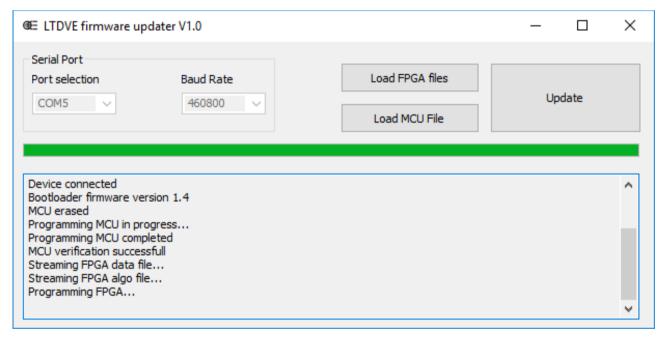

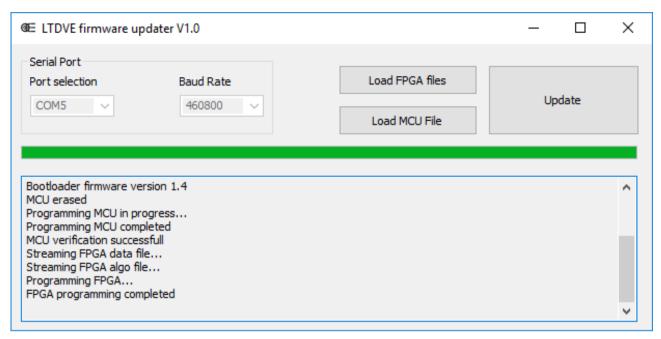

To activate the firmware update, follow these steps:

- 1. Switch off the device and wait 30 seconds

- 2. Push and hold down the INIT button

- 3. Switch on the device

- 4. Release the INIT button

- 5. Launch a firmware update (according to chapter 17) within 10 seconds.

Note the INIT button is sampled only once at power-up.

During the ten seconds interval, the RUN and ERR LEDs blink at a high rate to emphasize the circumstance. In the meantime, the use of the RS485 serial interface is restricted to the firmware update and the Modbus/TCP, Modbus/UDP, and HTTP protocols are not available.

The INIT button is concealed by a hole located between the USB port and the shell connector.

#### 12. Internal architecture

Each of the eight channels can be individually configured to output pulses based either on a discrete external trigger signal or an internally-generated trigger signal. A wide variety of internal triggers can be produced by configuring the internal pulse shaping logic.

This logic includes sixteen pulse generators and several multiplexers. The pulse generators allow pulse delay and width control down to 1 µs resolution. The multiplexers, organized as two routing matrices, allow for the flexible selection of the pulse generators inputs and outputs. The pulse generators can be excluded or bypassed when implementing continuous mode.

An output protection circuit, used to prevent the light from getting overheated and thus damaged, is also included in the logic.

### 12.1. Logic diagram

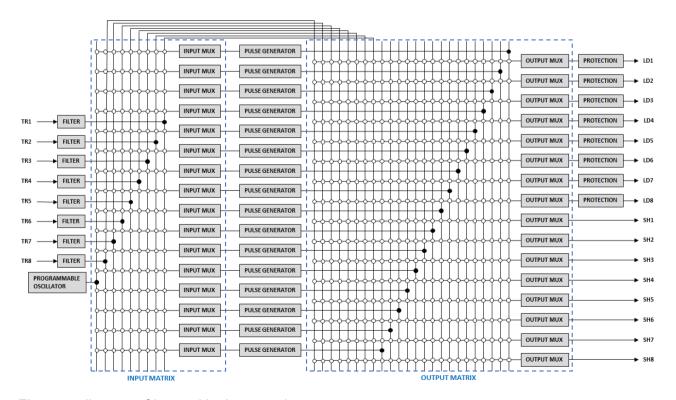

The drawing of *Figure 4: diagram of internal logic network* depicts the logic network built in the controller.

Figure 4: diagram of internal logic network

The eight synchronization inputs are shown at the left (TR1, TR2, TR3, TR4, TR5, TR6, TR7 and TR8), while the eight light outputs (LD1, LD2, LD3, LD4, LD5, LD6, LD7 and LD8) and the eight synchronization outputs (SH1, SH2, SH3, SH4, SH5, SH6, SH7 and SH8) are drawn at the right.

A description of each of the blocks is given in the next sections.

### 12.2. Input filters

The input filters are used to debounce and remove glitches from the incoming synchronization inputs. Each of the eight synchronization inputs has a dedicated, independent filter.

The algorithm implemented in each of the filters processes the relevant synchronization input with a finite state machine. A change in the filter output is performed only when the input signal has remained constant for a defined period of time, called filter time constant. Any pulses shorter than the filter time constant are thus removed and not passed through.

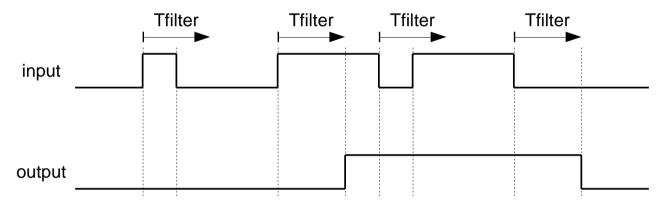

The diagram in *Figure 5: operation of the input filter* shows the filter operation on a random input signal.

Figure 5: operation of the input filter

As visible, the input signal is filtered by looking for pulses that hold the same state for a time of at least **Tfilter** before the change in state is passed to the output. Please note there is a fixed input to output propagation delay equal to this filter time constant.

Each of the eight filters can be set as follows:

- No filtering (pass through)

- Filtering with a 10µs time constant

- Filtering with a 20µs time constant

- Filtering with a 50µs time constant

- Filtering with a 100µs time constant

- Filtering with a 200µs time constant

- Filtering with a 500µs time constant

Setting of the filters can be done using the serial RS485 or Ethernet interfaces.

# 12.3. Input multiplexers

The input multiplexers are used to route the filtered inputs to the pulse generators. There are sixteen

input multiplexers organized in a 9x16 routing matrix.

Each multiplexer can have its output selected from one of the following sources:

- No selection

- Filtered synchronization input 1 (TR1)

- Filtered synchronization input 2 (TR2)

- Filtered synchronization input 3 (TR3)

- Filtered synchronization input 4 (TR4)

- Filtered synchronization input 5 (TR5)

- Filtered synchronization input 6 (TR6)

- Filtered synchronization input 7 (TR7)

- Filtered synchronization input 8 (TR8)

- · Free running oscillator

- Software trigger 1 (SW1)

- Software trigger 2 (SW2)

- Software trigger 3 (SW3)

- Software trigger 4 (SW4)

The free running oscillator is an autonomous asynchronous trigger source described in detail in the <u>chapter 12.7</u>. Setting of the input multiplexers can be done using the serial RS485 or Ethernet interfaces.

### 12.4. Pulse generator

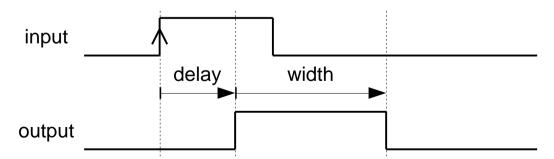

There are sixteen pulse generators. Each of them is characterized by two parameters: pulse delay, pulse width and hold off interval. The pulse delay can range from 0  $\mu$ s to 1,023,000  $\mu$ s with variable resolution down to 1  $\mu$ s. The pulse width can range from 1  $\mu$ s to 1,023,000  $\mu$ s with variable resolution down to 1  $\mu$ s. The hold off interval can range from 0  $\mu$ s to 1,023,000  $\mu$ s with variable resolution down to 1  $\mu$ s.

The diagram in *Figure 6: time diagram of pulse generator* describes the relationship between input and output. As depicted, the rising edge of the input signal triggers the generator, while the falling edge has no special meaning and can happen anywhere in time.

Figure 6: time diagram of pulse generator

Setting of the pulse generators can be done using the serial RS485 or Ethernet interfaces.

### 12.5. Output multiplexers

The output multiplexers are used to route the inner signals to the output stages. There are sixteen output multiplexers organized in a 24x16 routing matrix.

Each multiplexer can have its output selected from one of the following sources:

- No selection

- Pulse generator 1 output

- · Pulse generator 2 output

- Pulse generator 3 output

- Pulse generator 4 output

- Pulse generator 5 output

- Pulse generator 6 output

- Pulse generator 7 output

- Pulse generator 8 output

- Pulse generator 9 output

- Pulse generator 10 output

- Pulse generator 11 output

- Pulse generator 12 output

- Pulse generator 13 output

- Pulse generator 14 output

- Pulse generator 15 output

- Pulse generator 16 output

- Filtered synchronization input 1 (TR1)

- Filtered synchronization input 2 (TR2)

- Filtered synchronization input 3 (TR3)

- Filtered synchronization input 4 (TR4)

- Filtered synchronization input 5 (TR5)

- Filtered synchronization input 6 (TR6)

- Filtered synchronization input 7 (TR7)

- Filtered synchronization input 8 (TR8)

- Continuous

As visible in the internal logic network diagram (see *Figure 4: diagram of internal logic network*), the sixteen pulse generators can be entirely bypassed by selecting one of the eight filtered synchronization inputs (TR1, TR2, TR3, TR4, TR5, TR6, TR7 or TR8). Moreover, the outputs can operate continuously by selecting the **Continuous** option.

Setting of the output multiplexers can be done using the serial RS485 or Ethernet interfaces.

# 12.6. Output protection

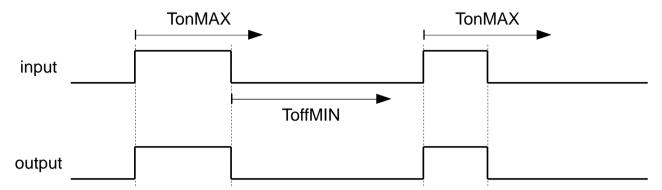

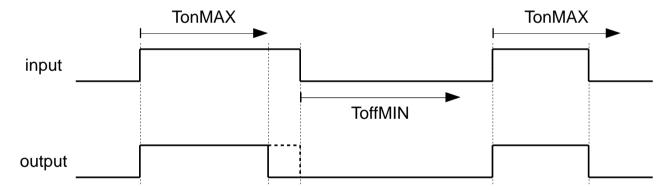

The output protection logic is used to prevent the light from getting overheated and thus damaged. Inside each of the eight protection blocks there is an independent state machine comprising a couple

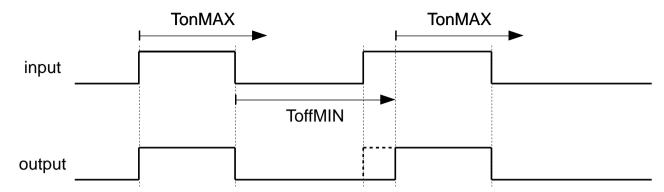

of timers. The first timer is used to constrain the turn-on time of the light (Ton) to be lesser than or equal to a programmable value **TonMAX**. The second timer is used to constrain the turn-off time of the light (Toff) to be greater than or equal to a programmable value **ToffMIN**.

The diagram in *Figure 7: turn-on and turn-off times within limits* shows what happens when both time constraints are satisfied. As visible in the diagram, the output follows the input.

Figure 7: turn-on and turn-off times within limits

The diagram in *Figure 8: protection prevents too long turn-on time* shows what happens when the turn-on time is too long. As visible in the diagram, the light is switched off at **TonMAX**, earlier than the original requirement.

Figure 8: protection prevents too long turn-on time

The diagram in *Figure 9: protection prevents too short turn-off time* shows what happens when turn-off time is too short. As visible in the diagram, the light is switched on at **ToffMIN**, later than the original requirement.

Figure 9: protection prevents too short turn-off time

The eight protection blocks are completely independent regarding to **TonMAX** (maximum turn-on time) and **ToffMIN** (minimum turn-off time). All of these time intervals can be programmed individually and may range from 1 ms to 255 ms in steps of 1 ms.

The turn-on protection can be inhibited on select outputs if a continuous operation is required by the application. Similarly, the turn-off protection can be inhibited on select outputs if required by the application.

Setting of the output protection logic can be done using the serial RS485 or Ethernet interfaces.

### 12.7. Free running oscillator

The free running oscillator is an autonomous asynchronous trigger source with a programmable period from 10 ms up to 1000 ms in steps of 1 ms (corresponding to a frequency of 100 Hz down to 1 Hz). It can be selected as an input to the input multiplexers.

Common usage of the oscillator is to test the lights during machine assembly and deployment.

# 13. Wiring diagrams

As discussed in the previous sections, the controller is quite flexible and many configurations can be achieved. The following wiring diagrams describe some of the most common.

# 13.1. Wiring example #1: controller triggers camera

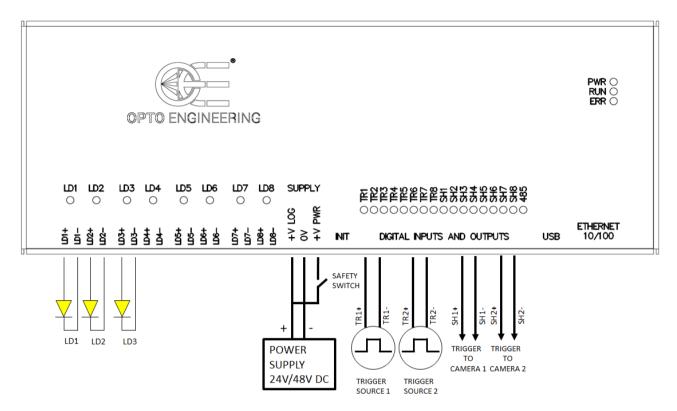

In the schematic diagram of *Figure 10: example schematic #1* the controller is driven by two input triggers, powers a total of three lights and triggers two cameras.

Figure 10: example schematic #1

As shown, the power and logic supplies are derived from a common power supply.

If required by the application, a safety switch may be included in the circuit to cut off supply to the power stages in order to protect the end user from photo-biological hazard. That switch would be appropriately placed on the machine chassis.

Cameras 1 and 2 are triggered by the controller using two of the eight available synchronization outputs. Generally, it is not possible to provide the details of the connections to the cameras because these are often vendor specific. Please see the camera hardware manual for more information.

# 13.2. Wiring example #2: camera triggers controller

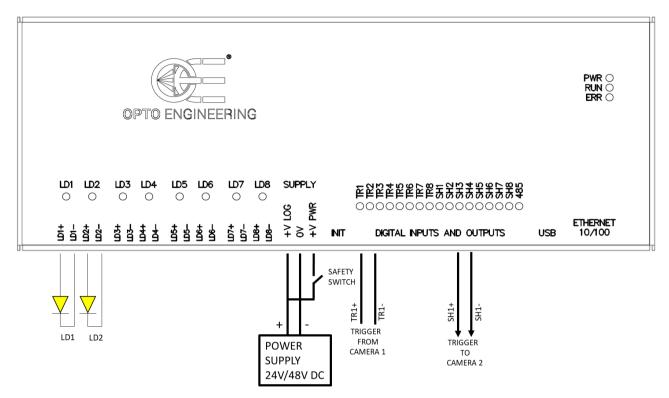

In the schematic diagram of *Figure 11: example schematic #2* the controller is driven by one input trigger coming from a camera, powers a total of two lights and triggers a second camera.

Figure 11: example schematic #2

As shown, the power and logic supplies are derived from a common power supply.

If required by the application, a safety switch may be included in the circuit to cut off supply to the power stages in order to protect the end user from photo-biological hazard. That switch would be appropriately placed on the machine chassis.

The controller is triggered by camera 1 using one of the eight available synchronization inputs. Camera 2 is triggered by the controller using one of the eight available synchronization outputs. Generally, it is not possible to provide the details of the connections to the cameras because these are often vendor specific. Please see the camera hardware manual for more information.

# 14. Operation

There are several ways to configure the controller.

A first option is to use the serial RS485 interface. To support this interface the controller implements a subset of the Modbus/RTU slave protocol. A second option is to use the Ethernet interface. Supported Ethernet speeds are 10 Mbit/s and 100 Mbit/s with auto negotiation. The Ethernet interface allows to configure the controller using the Modbus/TCP slave protocol, the Modbus/UDP slave protocol or the HTTP protocol. For supporting the latter, the controller provides an internal web server accessible by most common web browsers.

In the next sections, an overview of the Modbus/RTU, Modbus/TCP and Modbus/UDP protocols is given.

# 14.1. Operation with Modbus

The Modbus/RTU, Modbus/TCP and Modbus/UDP protocols are supported by most programmable logic controllers (PLCs) with a suitable communication port. The controller can also be configured by any PC with a proper interface.

Being simple and robust, over the years Modbus became a well-known communication protocol and

it is now a commonly available means of connecting industrial electronic devices. The development and update of Modbus protocols has been managed by the Modbus Organization since April 2004. The Modbus Organization is an association of users and suppliers of Modbus compliant devices that seeks to drive the adoption and evolution of Modbus.

The organization web site is:

#### http://www.modbus.org

More information, including Modbus specifications, implementation guides and code fragments can be downloaded from:

http://www.modbus.org/specs.php

### 14.1.1. Comparison of Modbus/RTU, Modbus/TCP and Modbus/UDP

The Modbus/RTU, Modbus/TCP and Modbus/UDP are pretty similar. The main difference is that Modbus/RTU is used on serial lines, while Modbus/TCP and Modbus/UDP are used on Ethernet connections. Modbus/TCP is connection-oriented and is implemented using TCP packets, while Modbus/UDP is connectionless and is implemented using UDP packets.

The controller implements Modbus/RTU with a serial RS485 interface (by default operating at 9600 bits per second, with even parity). The controller implements Modbus/TCP and Modbus/UDP with an Ethernet interface operating at 10 Mbit/s or 100 Mbit/s with auto negotiation.

### 14.1.2. Supported function codes

Modbus is a request/reply protocol and offers services specified by function codes.

The controller implements a restricted subset of the Modbus slave protocol. The list in *Table 16:* function codes supported by the controller summarizes the Modbus function codes supported by the controller with the current firmware.

| Function name            | Function code | Note |

|--------------------------|---------------|------|

| Read Holding Registers   | 0x03          |      |

| Write Single Register    | 0x06          |      |

| Write Multiple Registers | 0x10          |      |

Table 16: function codes supported by the controller

Any Modbus request containing an unimplemented function code is silently ignored by the controller and no response, of any kind, is given back to the master. These supported function codes can be used to access the controller internal register file, organized as an array of sixteen-bit (two bytes) values. These function codes are briefly described in the following sections.

# 14.1.3. Read Holding Registers (0x03)

This function code is used to read the contents of a contiguous block of registers from the controller register file. The master specifies the starting register address and the number of registers to be read. Registers are addressed starting at zero. The register data in the response message are packed as two bytes per register. For each register, the first byte contains the high order bits and the second contains the low order bits.

### 14.1.4. Write Single Register (0x06)

This function code is used to write a single register in the controller register file. The master specifies the address of the register to be written and the actual data to be written. Registers are addressed starting at zero. The register data in the request message are packed as two bytes per register. For each register, the first byte contains the high order bits and the second contains the low order bits. The normal response is an echo of the request, returned after the register contents have been written.

### 14.1.5. Write Multiple Registers (0x10)

This function code is used to write a block of contiguous registers (1 to 123 registers) in the controller register file. The master specifies the starting register address, the number of registers and the actual data to be written. Registers are addressed starting at zero. The register data in the request message are packed as two bytes per register. For each register, the first byte contains the high order bits and the second contains the low order bits. The normal response returns the function code, starting address, and quantity of registers written.

### 14.2. Register file

The list in *Table 17: controller register file* summarizes all the Modbus registers implemented in the controller. There are 512 registers, each of sixteen-bits (two bytes) in size. The registers are mapped at contiguous addresses starting at 0 and ending at 511.

| Address | Name          | Туре | Range       | Description                       |

|---------|---------------|------|-------------|-----------------------------------|

| 0       | DEVICE_TYPE   | R    | 0-<br>65535 | Device type                       |

| 1       | BOOT_VERSION  | R    | 0-<br>65535 | Bootloader firmware version       |

| 2       | MCU_VERSION   | R    | 0-<br>65535 | Microcontroller firmware version  |

| 3       | FPGA_VERSION  | R    | 0-<br>65535 | FPGA firmware version             |

| 4       | BOARD_VERSION | R    | 0-<br>65535 | Board version                     |

| 5       | OSC_PERIOD    | RW   | 10-<br>1000 | Period of the internal oscillator |

| 6       | FILTER_SEL0   | RW   | 0-6         | Filter setting for input TR1      |

| 7       | FILTER_SEL1   | RW   | 0-6         | Filter setting for input TR2      |

| 8       | FILTER_SEL2   | RW   | 0-6         | Filter setting for input TR3      |

| 9       | FILTER_SEL3   | RW   | 0-6         | Filter setting for input TR4      |

| 10      | FILTER_SEL4   | RW   | 0-6         | Filter setting for input TR5      |

| 11      | FILTER_SEL5   | RW   | 0-6         | Filter setting for input TR6      |

| 12      | FILTER_SEL6   | RW   | 0-6         | Filter setting for input TR7      |

| 13      | FILTER_SEL7   | RW   | 0-6         | Filter setting for input TR8      |

|    | INPUT SEL0       | RW | 0-         | Setting of input multiplexer 1                 |

|----|------------------|----|------------|------------------------------------------------|

| 14 | 1141 01_0220     | 1  | 4096       | Cotting of impartmentapioxol 1                 |

| 15 | INPUT_SEL1       | RW | 0-<br>4096 | Setting of input multiplexer 2                 |

| 16 | INPUT_SEL2       | RW | 0-<br>4096 | Setting of input multiplexer 3                 |

| 17 | INPUT_SEL3       | RW | 0-<br>4096 | Setting of input multiplexer 4                 |

| 18 | INPUT_SEL4       | RW | 0-<br>4096 | Setting of input multiplexer 5                 |

| 19 | INPUT_SEL5       | RW | 0-<br>4096 | Setting of input multiplexer 6                 |

| 20 | INPUT_SEL6       | RW | 0-<br>4096 | Setting of input multiplexer 7                 |

| 21 | INPUT_SEL7       | RW | 0-<br>4096 | Setting of input multiplexer 8                 |

| 22 | INPUT_SEL8       | RW | 0-<br>4096 | Setting of input multiplexer 9                 |

| 23 | INPUT_SEL9       | RW | 0-<br>4096 | Setting of input multiplexer 10                |

| 24 | INPUT_SEL10      | RW | 0-<br>4096 | Setting of input multiplexer 11                |

| 25 | INPUT_SEL11      | RW | 0-<br>4096 | Setting of input multiplexer 12                |

| 26 | INPUT_SEL12      | RW | 0-<br>4096 | Setting of input multiplexer 13                |

| 27 | INPUT_SEL13      | RW | 0-<br>4096 | Setting of input multiplexer 14                |

| 28 | INPUT_SEL14      | RW | 0-<br>4096 | Setting of input multiplexer 15                |

| 29 | INPUT_SEL15      | RW | 0-<br>4096 | Setting of input multiplexer 16                |

| 30 | GEN_DELAY_BASE0  | RW | 0-3        | Pulse delay time base selector for generator 1 |

| 31 | GEN_DELAY_COUNT0 | RW | 0-<br>1023 | Pulse delay setting for generator 1            |

| 32 | GEN_WIDTH_BASE0  | RW | 0-3        | Pulse width time base selector for generator 1 |

| 33 | GEN_WIDTH_COUNT0 | RW | 1-<br>1023 | Pulse width setting for generator 1            |

| 34 | GEN_DELAY_BASE1  | RW | 0-3        | Pulse delay time base selector for generator 2 |

| 35 | GEN_DELAY_COUNT1 | RW | 0-<br>1023 | Pulse delay setting for generator 2            |

|----|------------------|----|------------|------------------------------------------------|

| 36 | GEN_WIDTH_BASE1  | RW | 0-3        | Pulse width time base selector for generator 2 |

| 37 | GEN_WIDTH_COUNT1 | RW | 1-<br>1023 | Pulse width setting for generator 2            |

| 38 | GEN_DELAY_BASE2  | RW | 0-3        | Pulse delay time base selector for generator 3 |

| 39 | GEN_DELAY_COUNT2 | RW | 0-<br>1023 | Pulse delay setting for generator 3            |

| 40 | GEN_WIDTH_BASE2  | RW | 0-3        | Pulse width time base selector for generator 3 |

| 41 | GEN_WIDTH_COUNT2 | RW | 1-<br>1023 | Pulse width setting for generator 3            |

| 42 | GEN_DELAY_BASE3  | RW | 0-3        | Pulse delay time base selector for generator 4 |

| 43 | GEN_DELAY_COUNT3 | RW | 0-<br>1023 | Pulse delay setting for generator 4            |

| 44 | GEN_WIDTH_BASE3  | RW | 0-3        | Pulse width time base selector for generator 4 |

| 45 | GEN_WIDTH_COUNT3 | RW | 1-<br>1023 | Pulse width setting for generator 4            |

| 46 | GEN_DELAY_BASE4  | RW | 0-3        | Pulse delay time base selector for generator 5 |

| 47 | GEN_DELAY_COUNT4 | RW | 0-<br>1023 | Pulse delay setting for generator 5            |

| 48 | GEN_WIDTH_BASE4  | RW | 0-3        | Pulse width time base selector for generator 5 |

| 49 | GEN_WIDTH_COUNT4 | RW | 1-<br>1023 | Pulse width setting for generator 5            |

| 50 | GEN_DELAY_BASE5  | RW | 0-3        | Pulse delay time base selector for generator 6 |

| 51 | GEN_DELAY_COUNT5 | RW | 0-<br>1023 | Pulse delay setting for generator 6            |

| 52 | GEN_WIDTH_BASE5  | RW | 0-3        | Pulse width time base selector for generator 6 |

| 53 | GEN_WIDTH_COUNT5 | RW | 1-<br>1023 | Pulse width setting for generator 6            |

| 54 | GEN_DELAY_BASE6  | RW | 0-3        | Pulse delay time base selector for generator 7 |

| 55 | GEN_DELAY_COUNT6 | RW | 0-<br>1023 | Pulse delay setting for generator 7            |

| 56 | GEN_WIDTH_BASE6   | RW | 0-3        | Pulse width time base selector for generator 7  |

|----|-------------------|----|------------|-------------------------------------------------|

| 57 | GEN_WIDTH_COUNT6  | RW | 1-<br>1023 | Pulse width setting for generator 7             |

| 58 | GEN_DELAY_BASE7   | RW | 0-3        | Pulse delay time base selector for generator 8  |

| 59 | GEN_DELAY_COUNT7  | RW | 0-<br>1023 | Pulse delay setting for generator 8             |

| 60 | GEN_WIDTH_BASE7   | RW | 0-3        | Pulse width time base selector for generator 8  |

| 61 | GEN_WIDTH_COUNT7  | RW | 1-<br>1023 | Pulse width setting for generator 8             |

| 62 | GEN_DELAY_BASE8   | RW | 0-3        | Pulse delay time base selector for generator 9  |

| 63 | GEN_DELAY_COUNT8  | RW | 0-<br>1023 | Pulse delay setting for generator 9             |

| 64 | GEN_WIDTH_BASE8   | RW | 0-3        | Pulse width time base selector for generator 9  |

| 65 | GEN_WIDTH_COUNT8  | RW | 1-<br>1023 | Pulse width setting for generator 9             |

| 66 | GEN_DELAY_BASE9   | RW | 0-3        | Pulse delay time base selector for generator 10 |

| 67 | GEN_DELAY_COUNT9  | RW | 0-<br>1023 | Pulse delay setting for generator 10            |

| 68 | GEN_WIDTH_BASE9   | RW | 0-3        | Pulse width time base selector for generator 10 |

| 69 | GEN_WIDTH_COUNT9  | RW | 1-<br>1023 | Pulse width setting for generator 10            |

| 70 | GEN_DELAY_BASE10  | RW | 0-3        | Pulse delay time base selector for generator 11 |

| 71 | GEN_DELAY_COUNT10 | RW | 0-<br>1023 | Pulse delay setting for generator 11            |

| 72 | GEN_WIDTH_BASE10  | RW | 0-3        | Pulse width time base selector for generator 11 |

| 73 | GEN_WIDTH_COUNT10 | RW | 1-<br>1023 | Pulse width setting for generator 11            |

| 74 | GEN_DELAY_BASE11  | RW | 0-3        | Pulse delay time base selector for generator 12 |

| 75 | GEN_DELAY_COUNT11 | RW | 0-<br>1023 | Pulse delay setting for generator 12            |

| 76 | GEN_WIDTH_BASE11  | RW | 0-3        | Pulse width time base selector for generator 12 |

| 77 | GEN_WIDTH_COUNT11  | RW | 1-<br>1023  | Pulse width setting for generator 12                  |

|----|--------------------|----|-------------|-------------------------------------------------------|

| 78 | GEN_DELAY_BASE12   | RW | 0-3         | Pulse delay time base selector for generator 13       |

| 79 | GEN_DELAY_COUNT12  | RW | 0-<br>1023  | Pulse delay setting for generator 13                  |

| 80 | GEN_WIDTH_BASE12   | RW | 0-3         | Pulse width time base selector for generator 13       |

| 81 | GEN_WIDTH_COUNT012 | RW | 1-<br>1023  | Pulse width setting for generator 13                  |

| 82 | GEN_DELAY_BASE13   | RW | 0-3         | Pulse delay time base selector for generator 14       |

| 83 | GEN_DELAY_COUNT13  | RW | 0-<br>1023  | Pulse delay setting for generator 14                  |

| 84 | GEN_WIDTH_BASE13   | RW | 0-3         | Pulse width time base selector for generator 14       |

| 85 | GEN_WIDTH_COUNT13  | RW | 1-<br>1023  | Pulse width setting for generator 14                  |

| 86 | GEN_DELAY_BASE14   | RW | 0-3         | Pulse delay time base selector for generator 15       |

| 87 | GEN_DELAY_COUNT14  | RW | 0-<br>1023  | Pulse delay setting for generator 15                  |

| 88 | GEN_WIDTH_BASE14   | RW | 0-3         | Pulse width time base selector for generator 15       |

| 89 | GEN_WIDTH_COUNT14  | RW | 1-<br>1023  | Pulse width setting for generator 15                  |

| 90 | GEN_DELAY_BASE15   | RW | 0-3         | Pulse delay time base selector for generator 16       |

| 91 | GEN_DELAY_COUNT15  | RW | 0-<br>1023  | Pulse delay setting for generator 16                  |

| 92 | GEN_WIDTH_BASE15   | RW | 0-3         | Pulse width time base selector for generator 16       |

| 93 | GEN_WIDTH_COUNT15  | RW | 1-<br>1023  | Pulse width setting for generator 16                  |

| 94 | OUTPUT_SEL_HI0     | RW | 0-256       | High order byte of setting for LD1 output multiplexer |

| 95 | OUTPUT_SEL_LO0     | RW | 0-<br>32768 | Low order byte of setting for LD1 output multiplexer  |

| 96 | OUTPUT_SEL_HI1     | RW | 0-256       | High order byte of setting for LD2 output multiplexer |

| 97 | OUTPUT_SEL_LO1     | RW | 0-<br>32768 | Low order byte of setting for LD2 output multiplexer  |

| 98  | OUTPUT_SEL_HI2  | RW | 0-256       | High order byte of setting for LD3 output multiplexer |

|-----|-----------------|----|-------------|-------------------------------------------------------|

| 99  | OUTPUT_SEL_LO2  | RW | 0-<br>32768 | Low order byte of setting for LD3 output multiplexer  |

| 100 | OUTPUT_SEL_HI3  | RW | 0-256       | High order byte of setting for LD4 output multiplexer |

| 101 | OUTPUT_SEL_LO3  | RW | 0-<br>32768 | Low order byte of setting for LD4 output multiplexer  |

| 102 | OUTPUT_SEL_HI4  | RW | 0-256       | High order byte of setting for LD5 output multiplexer |

| 103 | OUTPUT_SEL_LO4  | RW | 0-<br>32768 | Low order byte of setting for LD5 output multiplexer  |

| 104 | OUTPUT_SEL_HI5  | RW | 0-256       | High order byte of setting for LD6 output multiplexer |

| 105 | OUTPUT_SEL_LO5  | RW | 0-<br>32768 | Low order byte of setting for LD6 output multiplexer  |

| 106 | OUTPUT_SEL_HI6  | RW | 0-256       | High order byte of setting for LD7 output multiplexer |

| 107 | OUTPUT_SEL_LO6  | RW | 0-<br>32768 | Low order byte of setting for LD7 output multiplexer  |

| 108 | OUTPUT_SEL_HI7  | RW | 0-256       | High order byte of setting for LD8 output multiplexer |

| 109 | OUTPUT_SEL_LO7  | RW | 0-<br>32768 | Low order byte of setting for LD8 output multiplexer  |

| 110 | OUTPUT_SEL_HI8  | RW | 0-256       | High order byte of setting for SH1 output multiplexer |

| 111 | OUTPUT_SEL_LO8  | RW | 0-<br>32768 | Low order byte of setting for SH1 output multiplexer  |

| 112 | OUTPUT_SEL_HI9  | RW | 0-256       | High order byte of setting for SH2 output multiplexer |

| 113 | OUTPUT_SEL_LO9  | RW | 0-<br>32768 | Low order byte of setting for SH2 output multiplexer  |

| 114 | OUTPUT_SEL_HI10 | RW | 0-256       | High order byte of setting for SH3 output multiplexer |

| 115 | OUTPUT_SEL_LO10 | RW | 0-<br>32768 | Low order byte of setting for SH3 output multiplexer  |

| 116 | OUTPUT_SEL_HI11 | RW | 0-256       | High order byte of setting for SH4 output multiplexer |

| 117 | OUTPUT_SEL_LO11 | RW | 0-<br>32768 | Low order byte of setting for SH4 output multiplexer  |

| 118 | OUTPUT_SEL_HI12 | RW | 0-256       | High order byte of setting for SH5 output multiplexer |

| 119 | OUTPUT_SEL_LO12 | RW | 0-<br>32768 | Low order byte of setting for SH5 output multiplexer            |

|-----|-----------------|----|-------------|-----------------------------------------------------------------|

| 120 | OUTPUT_SEL_HI13 | RW | 0-256       | High order byte of setting for SH6 output multiplexer           |

| 121 | OUTPUT_SEL_LO13 | RW | 0-<br>32768 | Low order byte of setting for SH6 output multiplexer            |

| 122 | OUTPUT_SEL_HI14 | RW | 0-256       | High order byte of setting for SH7 output multiplexer           |

| 123 | OUTPUT_SEL_LO14 | RW | 0-<br>32768 | Low order byte of setting for SH7 output multiplexer            |

| 124 | OUTPUT_SEL_HI15 | RW | 0-256       | High order byte of setting for SH8 output multiplexer           |

| 125 | OUTPUT_SEL_LO15 | RW | 0-<br>32768 | Low order byte of setting for SH8 output multiplexer            |

| 126 | PRT_CNT_ON0     | RW | 1-255       | Maximum turn-on time for light output LD1                       |

| 127 | PRT_ENA_ON0     | RW | 0-1         | Enable limitation of maximum turn-on time for light output LD1  |

| 128 | PRT_CNT_OFF0    | RW | 1-255       | Minimum turn-off time for light output LD1                      |

| 129 | PRT_ENA_OFF0    | RW | 0-1         | Enable limitation of minimum turn-off time for light output LD1 |

| 130 | PRT_CNT_ON1     | RW | 1-255       | Maximum turn-on time for light output LD2                       |

| 131 | PRT_ENA_ON1     | RW | 0-1         | Enable limitation of maximum turn-on time for light output LD2  |

| 132 | PRT_CNT_OFF1    | RW | 1-255       | Minimum turn-off time for light output LD2                      |

| 133 | PRT_ENA_OFF1    | RW | 0-1         | Enable limitation of minimum turn-off time for light output LD2 |

| 134 | PRT_CNT_ON2     | RW | 1-255       | Maximum turn-on time for light output LD3                       |

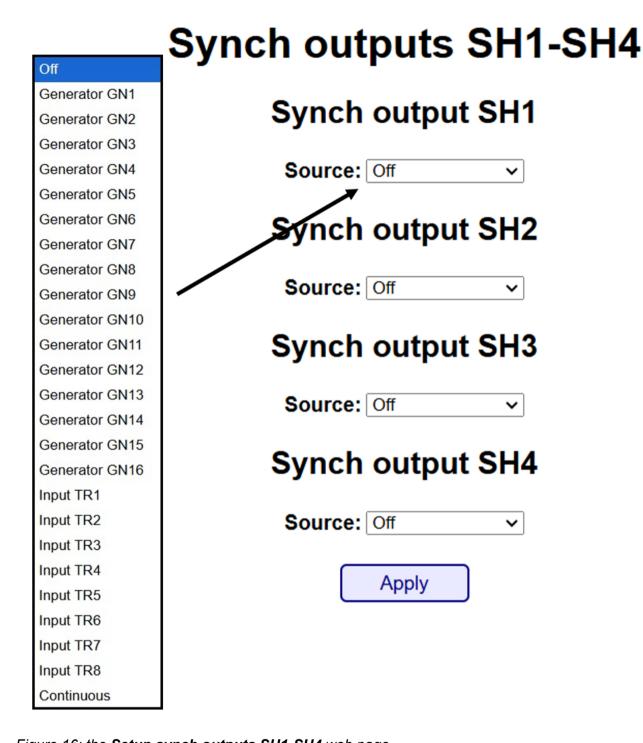

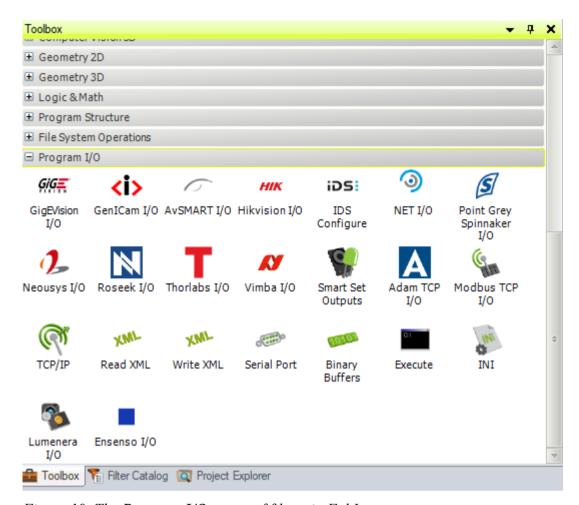

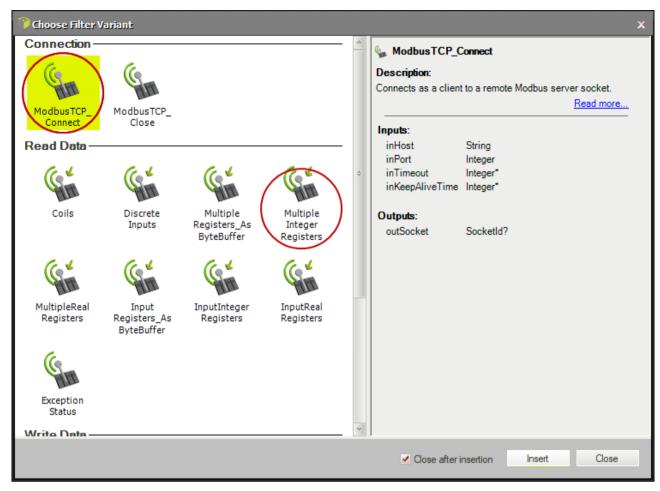

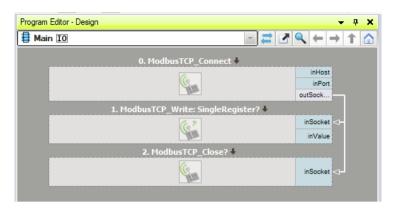

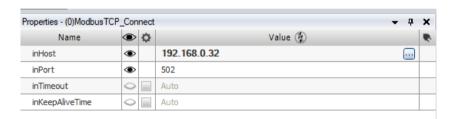

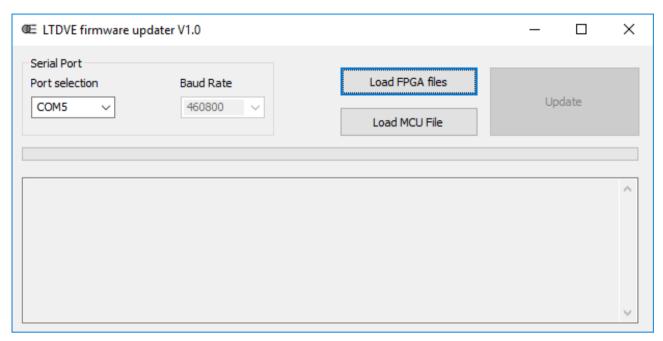

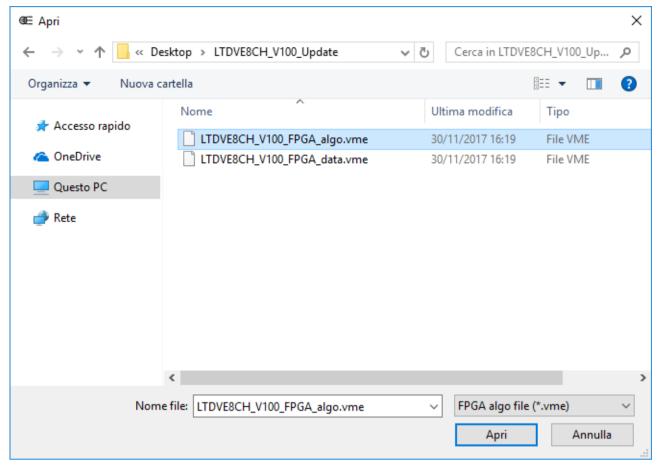

| 135 | PRT_ENA_ON2     | RW | 0-1         | Enable limitation of maximum turn-on time for light output LD3  |